常用EDA工具之Tanner集成电路设计软件 功能与应用

在集成电路设计领域,电子设计自动化工具扮演着至关重要的角色。其中,Tanner系列软件作为一款历史悠久的EDA工具,以其在特定应用场景下的优势,成为许多工程师和研究机构的重要选择。

一、Tanner工具概述

Tanner工具最初由Tanner Research公司开发,现已成为Mentor Graphics(现为Siemens EDA)产品线的一部分。它主要面向模拟/混合信号集成电路设计、微机电系统设计和光电集成设计,尤其在教学、科研和小规模芯片设计中广受欢迎。

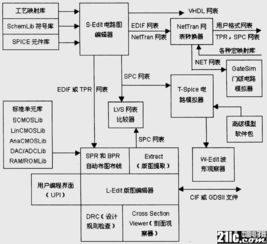

二、核心模块与功能

Tanner工具套件包含多个核心模块:

- L-Edit:版图编辑工具,提供直观的图形界面,支持层次化设计,能够处理复杂的多边形编辑,是Tanner工具中最著名的模块。

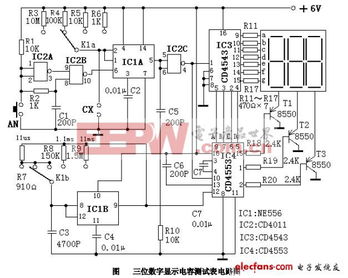

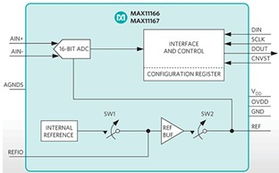

- T-Spice:电路仿真器,支持SPICE语言,能够进行瞬态分析、直流分析、交流分析和噪声分析等。

- S-Edit:原理图捕获工具,用于绘制电路原理图并生成网表。

- HiPer Verify:设计规则检查和版图与原理图一致性检查工具。

- Calibre:与Mentor的Calibre工具集成,提供更强大的物理验证功能。

三、应用优势

- 学习门槛较低:相比一些大型EDA工具,Tanner的界面相对简洁,更适合初学者掌握集成电路设计的基本流程。

- 成本效益高:对于学术机构和小型设计团队,Tanner提供了相对经济的解决方案。

- 灵活性强:支持自定义设计规则和器件模型,能够适应各种特殊工艺需求。

- 混合信号设计支持:在模拟和混合信号电路设计方面表现突出。

四、典型设计流程

使用Tanner进行集成电路设计的典型流程包括:

- 电路设计:在S-Edit中绘制原理图,定义电路拓扑结构。

- 电路仿真:将原理图网表导入T-Spice,添加激励和模型参数,进行性能仿真和优化。

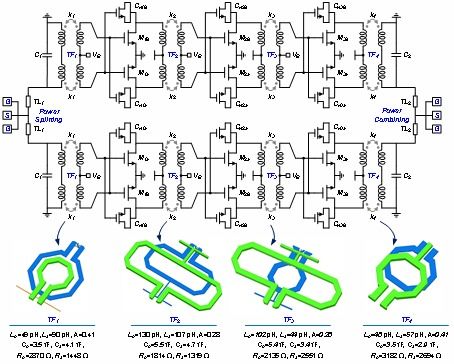

- 版图设计:在L-Edit中根据工艺设计规则绘制物理版图,实现电路到几何图形的转换。

- 物理验证:使用HiPer Verify或Calibre进行DRC和LVS检查,确保版图符合制造要求。

- 后仿真:提取版图寄生参数,进行带寄生效应的电路仿真,验证最终性能。

五、在行业中的定位

虽然Tanner在高端数字芯片设计和大规模集成电路设计方面可能不如Cadence、Synopsys等工具全面,但它在教育领域、模拟/混合信号芯片设计、MEMS设计和快速原型开发方面具有独特优势。许多大学将其作为集成电路设计入门课程的教学工具,而一些公司则用它进行特定类型的芯片设计。

六、发展趋势

随着Siemens EDA对Tanner工具的持续投入,它正不断集成更先进的功能,如与Mentor其他工具的深度整合、云平台支持以及对新兴工艺节点的适配。它保持了在易用性和特定应用领域的传统优势。

Tanner集成电路设计工具以其独特的定位和功能,在EDA工具生态系统中占据着不可替代的地位。对于学习集成电路设计的学生、从事模拟/混合信号设计的工程师以及需要快速原型开发的团队来说,它仍然是一个值得考虑的优秀工具选择。

如若转载,请注明出处:http://www.yunguochuxing.com/product/70.html

更新时间:2026-02-25 06:31:04